Tehnička dokumentacija

Tehnički podaci

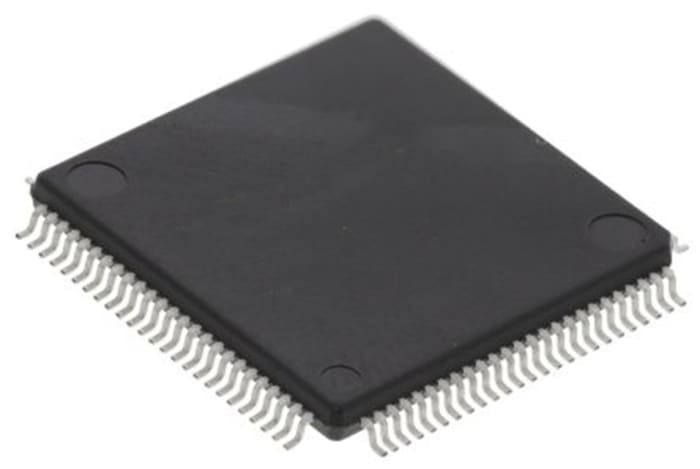

Brand

Renesas ElectronicsFamily Name

RX

Package Type

LQFP

Mounting Type

Surface Mount

Pin Count

100

Device Core

RX

Data Bus Width

32bit

Program Memory Size

768 kB

Maximum Frequency

100MHz

RAM Size

128 kB

USB Channels

1

Number of SPI Channels

11

Number of USART Channels

0

Typical Operating Supply Voltage

2.7 → 3.6 V

Number of CAN Channels

0

Number of I2C Channels

11

Number of UART Channels

9

Dimensions

14.1 x 14.1 x 1.55mm

Width

14.1mm

Height

1.55mm

Number of LIN Channels

0

Number of Ethernet Channels

0

Number of PCI Channels

0

Maximum Operating Temperature

+85 °C

Instruction Set Architecture

CISC

Maximum Number of Ethernet Channels

0

ADCs

1 (14 x 12 bit)

Length

14.1mm

Number of ADC Units

1

Program Memory Type

Flash

Minimum Operating Temperature

-40 °C

Zemlja podrijetla

Japan

Detalji o proizvodu

RX630 Microcontrollers

The RX630 family of 32-bit microcontrollers features 100MHz high-speed operation and large-capacity on-chip memory.

Cena na upit

Standard

1

Cena na upit

Standard

1

Informacije o stanju skladišta trenutno nisu dostupne.

Proverite ponovno kasnije.

Tehnička dokumentacija

Tehnički podaci

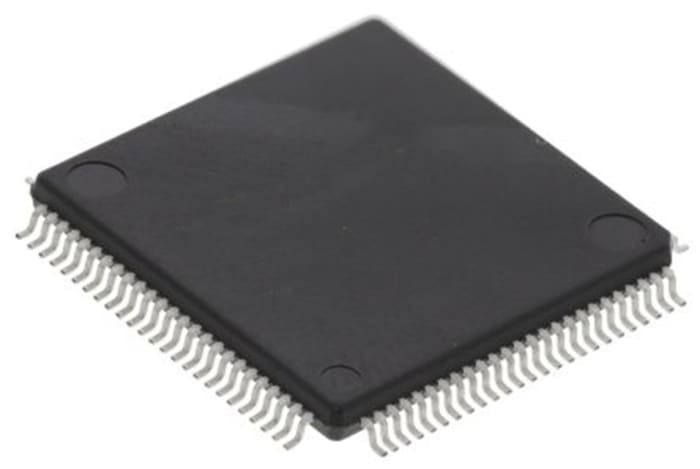

Brand

Renesas ElectronicsFamily Name

RX

Package Type

LQFP

Mounting Type

Surface Mount

Pin Count

100

Device Core

RX

Data Bus Width

32bit

Program Memory Size

768 kB

Maximum Frequency

100MHz

RAM Size

128 kB

USB Channels

1

Number of SPI Channels

11

Number of USART Channels

0

Typical Operating Supply Voltage

2.7 → 3.6 V

Number of CAN Channels

0

Number of I2C Channels

11

Number of UART Channels

9

Dimensions

14.1 x 14.1 x 1.55mm

Width

14.1mm

Height

1.55mm

Number of LIN Channels

0

Number of Ethernet Channels

0

Number of PCI Channels

0

Maximum Operating Temperature

+85 °C

Instruction Set Architecture

CISC

Maximum Number of Ethernet Channels

0

ADCs

1 (14 x 12 bit)

Length

14.1mm

Number of ADC Units

1

Program Memory Type

Flash

Minimum Operating Temperature

-40 °C

Zemlja podrijetla

Japan

Detalji o proizvodu

RX630 Microcontrollers

The RX630 family of 32-bit microcontrollers features 100MHz high-speed operation and large-capacity on-chip memory.